ECL (logic ghép nối bộ phát) lần đầu tiên được phát minh tại IBM vào tháng 8 năm 1956 bởi Hannon S. Yourke. Logic này còn được gọi là logic chế độ hiện tại, được sử dụng trong các máy tính của IBM 7090 & 7094. Họ ECL rất nhanh so với logic kỹ thuật số các gia đình. Nói chung, họ logic này cung cấp độ trễ lan truyền nhỏ hơn 1 ns. Nó là một họ logic dựa trên các bóng bán dẫn mối nối lưỡng cực. Đây là mạch họ logic nhanh nhất có thể truy cập để thiết kế một hệ thống logic thông thường. Bài viết này thảo luận tổng quan về một mạch logic kết hợp bộ phát , làm việc với các ứng dụng.

Emitter Coupled Logic là gì?

Logic được ghép nối với máy phát là tốt nhất BJT họ logic dựa trên được sử dụng trong thiết kế hệ thống logic thông thường. Đôi khi, nó còn được gọi là logic chế độ hiện tại, là một công nghệ kỹ thuật số tốc độ rất cao. Nói chung, ECL được coi là vi mạch logic nhanh nhất, nơi nó đạt được hoạt động tốc độ cao bằng cách sử dụng một dao động điện áp rất nhỏ và cũng tránh các bóng bán dẫn đi vào vùng bão hòa.

Việc triển khai ECL sử dụng điện áp cung cấp dương được gọi là PECL hoặc ECL tham chiếu tích cực. Trong các cổng ECL ban đầu, nguồn điện áp âm được sử dụng do khả năng chống nhiễu. Sau đó, ECL tham chiếu tích cực trở nên rất nổi tiếng do mức logic tương thích hơn của nó so với họ logic TTL.

Lôgic kết hợp bộ phát tiêu tán một lượng lớn công suất tĩnh, tuy nhiên, mức tiêu thụ dòng điện tổng thể của nó thấp hơn so với CMOS ở tần số cao. Vì vậy, ECL chủ yếu có lợi trong các mạch phân phối xung nhịp và các ứng dụng dựa trên tần số cao.

Các tính năng logic của Emitter Coupled

Các tính năng của ECL sẽ làm cho chúng được sử dụng trong nhiều ứng dụng dựa trên hiệu suất cao.

- ECL cung cấp hai đầu ra luôn bổ sung cho nhau vì hoạt động của mạch dựa trên bộ khuếch đại vi sai.

- Họ logic này chủ yếu phù hợp với các phương pháp chế tạo nguyên khối vì các mức logic là một hàm của tỷ số điện trở.

- Các thiết bị thuộc họ ECL tạo ra đầu ra phù hợp & bổ sung của chức năng được đề xuất mà không cần sử dụng bất kỳ bộ biến tần bên ngoài nào. Do đó, nó làm giảm số lượng gói, yêu cầu năng lượng và cũng giảm các vấn đề xảy ra do sự chậm trễ thời gian.

- Các thiết bị ECL trong thiết kế bộ khuếch đại vi sai cung cấp tính linh hoạt về hiệu suất rộng rãi, vì vậy các mạch ECL cho phép được sử dụng cả như mạch kỹ thuật số và mạch tuyến tính.

- Thiết kế của cổng ECL thường có trở kháng đầu vào cao và thấp, điều này cực kỳ có lợi để đạt được khả năng quạt ra lớn cũng như truyền động.

- Thiết bị ECL tạo ra dòng điện không đổi trên nguồn điện để đơn giản hóa việc thiết kế nguồn điện.

- Các thiết bị của ECL bao gồm đầu ra bộ phát mở chỉ đơn giản cho phép chúng bao gồm dung lượng ổ đĩa đường truyền.

Mạch lôgic ghép bộ phát

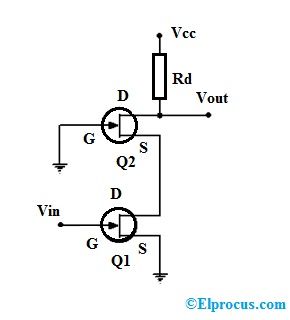

Mạch logic kết hợp bộ phát cho biến tần được hiển thị bên dưới được thiết kế với các điện trở và bóng bán dẫn. Trong mạch này, các cực phát của hai bóng bán dẫn được kết nối đơn giản với điện trở hạn chế dòng điện RE được sử dụng để tránh bóng bán dẫn đi vào trạng thái bão hòa. Ở đây đầu ra của bóng bán dẫn được lấy từ đầu cực thu thay vì đầu cực phát. Mạch này cung cấp hai đầu ra Vout (đầu ra đảo ngược) và Vout2 (đầu ra không đảo) và thiết bị đầu cuối đầu vào như Vin nơi đầu vào cao hoặc thấp được đưa ra. + Vcc = 5V.

Logic ghép nối Emitter hoạt động như thế nào?

Hoạt động của logic kết hợp bộ phát là, bất cứ khi nào đầu vào CAO được cấp cho mạch ECL, thì nó sẽ làm cho bóng bán dẫn ‘Q1’ BẬT và bóng bán dẫn Q2 TẮT nhưng bóng bán dẫn Q1 không bão hòa. Vì vậy, điều này sẽ kéo đầu ra VOUT2 lên CAO và giá trị của đầu ra VOUT1 sẽ THẤP vì sụt giảm trong R1.

Tương tự, khi giá trị VIN được cấp cho ECL là THẤP, thì nó sẽ làm cho bóng bán dẫn Q1 TẮT & bóng bán dẫn Q2 BẬT. Vì vậy, bóng bán dẫn Q2 sẽ không chuyển sang trạng thái bão hòa. Vì vậy, nó sẽ làm cho đầu ra VOUT1 được kéo giá trị CAO và giá trị đầu ra VOUT2 sẽ thấp do giảm trong điện trở R2.

Hãy xem bóng bán dẫn Q1 và Q2 bật và tắt như thế nào khi có điện áp được đặt vào.

Hai bóng bán dẫn như Q1 & Q2 trong mạch này được kết nối như một bộ khuếch đại vi sai bằng một điện trở phát chung.

Nguồn cung cấp điện áp cho mạch ví dụ này là VCC = 5.0, VBB = 4.0 & VEE = 0 V. Giá trị mức CAO & THẤP đầu vào được xác định đơn giản là 4,4 V & 3,6V. Trên thực tế, mạch này tạo ra mức đầu ra THẤP & mức CAO cao hơn 0,6 Vôn; tuy nhiên, điều này được sửa chữa trong các mạch ECL thực.

Khi Vin ở mức CAO, thì bóng bán dẫn Q1 được bật, tuy nhiên không bão hòa và bóng bán dẫn Q2 bị tắt. Vì vậy, điện áp đầu ra như VOUT2 được kéo đến 5 V thông qua điện trở R2 và nó có thể được chứng minh rằng điện áp giảm trên điện trở R1 là khoảng 0,8 V để VOUT1 = 4,2 V (THẤP). Ngoài ra VE = VOUT1 - VQ1 => 4.2V - 0.4V = 3.8V khi transistor Q1 được BẬT hoàn toàn.

Khi Vin ở mức THẤP, bóng bán dẫn Q2 sẽ được bật, nhưng không bão hòa và bóng bán dẫn Q1 bị TẮT. Do đó, VOUT1 được kéo đến 5,0 V bằng cách sử dụng một điện trở R1 & nó có thể được hiển thị rằng VOUT2 là 4,2 V. Ngoài ra VE => VOUT2 - VQ2 => 4,2V - 0,8V => 3,4V khi bóng bán dẫn Q2 được BẬT.

Trong ECL, hai bóng bán dẫn không bao giờ bão hòa khi t anh ta thay đổi điện áp đầu vào / đầu ra khá nhỏ như 0,8v và trở kháng đầu vào cao và trở kháng đầu ra thấp. Điều này giúp ECL hoạt động nhanh hơn với thời gian trễ truyền ít hơn.

Hai đầu vào phát ra kết hợp mạch cổng logic OR / NOR

Hai mạch cổng logic OR / NOR kết hợp bộ phát đầu vào được hiển thị bên dưới. Mạch này được thiết kế bằng cách sửa đổi mạch nghịch lưu trên. Việc sửa đổi là bằng cách thêm một bóng bán dẫn phụ ở phía đầu vào.

Hoạt động của mạch này rất đơn giản. Khi các đầu vào được áp dụng cho cả hai bóng bán dẫn Q1 và Q2 thấp thì sẽ làm cho đầu ra1 (Vout1) có giá trị CAO. Vì vậy, Vout1 này tương đương với đầu ra của cổng NOR.

Đồng thời, nếu bóng bán dẫn Q3 được BẬT, thì nó sẽ làm cho đầu ra thứ hai (Vout2) ở mức CAO. Vì vậy, đầu ra Vou2 này tương ứng với đầu ra cổng OR.

Theo cách tương tự, nếu cả đầu vào bóng bán dẫn Q1 & Q2 đều ở mức CAO, thì nó sẽ bật bóng bán dẫn Q1 & Q2 và cung cấp đầu ra thấp ở đầu cuối VOUT1.

Nếu bóng bán dẫn Q3 bị TẮT trong suốt hoạt động này thì nó sẽ cung cấp đầu ra cao ở đầu cuối VOUT2. Vì vậy, bảng sự thật cho cổng OR / NOR được đưa ra dưới đây.

|

Đầu vào |

Đầu vào | HOẶC |

CŨNG KHÔNG |

|

Một |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Các đặc điểm logic được ghép nối với máy phát

Các đặc điểm của ECL bao gồm những điều sau đây.

- So với TTL, ECL có thời gian lan truyền nhanh hơn, dao động từ 0,5 đến 2 ns. Tuy nhiên, mức tiêu tán công suất logic kết hợp với bộ phát cao hơn so với TTL như 30 mW.

- Điện áp I / O của ECL có một dao động nhỏ như 0,8.

- Trở kháng đầu vào của ECL cao & điện trở đầu ra thấp; do đó, bóng bán dẫn thay đổi trạng thái của nó rất nhanh.

- Công suất quạt ra của ECL cao và độ trễ cổng thấp.

- Logic o / p của ECL thay đổi từ trạng thái THẤP đến CAO nhưng mức điện áp cho các trạng thái này sẽ khác nhau giữa TTL & EC.

- Khả năng chống ồn của ECL là 0,4V.

Ưu điểm và nhược điểm

Các lợi thế của logic ghép nối bộ phát được thảo luận dưới đây.

- Fanout của ECL là 25 tốt hơn so với TTL & nó thấp hơn so với CMOS.

- Thời gian trễ truyền trung bình của ECL là 1 đến 4 ns, tốt hơn so với cả CMOS &

- TTL. Vì vậy nó được gọi là họ logic nhanh nhất.

- Khi các BJT trong bộ phát được kết hợp cổng logic hoạt động trong vùng hoạt động, khi đó chúng có tốc độ tối đa so với tất cả các họ logic.

- Cổng ECL tạo ra các đầu ra bổ sung.

- Các xung chuyển mạch hiện tại không có trong các dây dẫn cung cấp điện.

- Các đầu ra có thể được ghép nối với nhau để cung cấp chức năng OR có dây.

- Các thông số của ECL không thay đổi nhiều qua nhiệt độ.

- Không. của các chức năng có thể truy cập được từ một con chip duy nhất là cao.

Các nhược điểm của logic ghép nối bộ phát được thảo luận dưới đây.

- Nó có biên độ ồn cực kỳ ít hơn, tức là ± 200 mV.

- Công suất tiêu tán cao so với các cổng logic khác.

- Để giao tiếp với các họ logic khác, các bộ chuyển mức là cần thiết.

- Fanout giới hạn tải điện dung.

- So với TTL , Cổng ECL đắt tiền.

- So với CMOS & TTL, khả năng chống ồn ECL kém nhất.

Các ứng dụng

Các ứng dụng của logic ghép nối bộ phát bao gồm những điều sau đây.

- Logic ghép nối bộ phát được sử dụng như một công nghệ logic & giao diện trong các thiết bị truyền thông tốc độ cực cao như giao diện bộ thu phát sợi quang, mạng Ethernet & ATM (Chế độ truyền không đồng bộ).

- ECL là một họ logic dựa trên BJT nơi hoạt động tốc độ cao của nó có thể đạt được bằng cách sử dụng dao động điện áp tương đối nhỏ & tránh các bóng bán dẫn di chuyển vào vùng bão hòa.

- ECL được sử dụng để tạo mạch ASLT trong IBM 360/91.

- ECL tránh việc sử dụng các bóng bán dẫn xếp chồng lên nhau bằng cách sử dụng i / p phân cực một đầu và phản hồi tích cực giữa các bóng bán dẫn sơ cấp và thứ cấp để đạt được chức năng biến tần.

- ECL được sử dụng trong thiết bị điện tử tốc độ cực cao.

Vì vậy, đây là tổng quan về logic kết hợp bộ phát hoặc ECL - mạch, hoạt động, tính năng, đặc điểm và ứng dụng. ECL là họ logic nhanh nhất dựa trên BJT so với các họ logic kỹ thuật số khác. Nó đạt được tốc độ hoạt động tối đa bằng cách sử dụng một dao động điện áp nhỏ và tránh các bóng bán dẫn di chuyển vào vùng bão hòa. Họ logic này cung cấp độ trễ lan truyền 1ns đáng kinh ngạc và trong các họ ECL mới nhất, độ trễ này giảm xuống. Đây là một câu hỏi dành cho bạn, tên thay thế cho ECL là gì?