ARM (Máy RISC nâng cao) đã đưa ra một số bộ vi xử lý có các tính năng khác nhau cũng như các lõi khác nhau cho nhiều ứng dụng khác nhau. Thiết kế kiến trúc ARM đầu tiên có bộ xử lý 26-bit, nhưng bây giờ nó đã đạt đến bộ xử lý 64-bit. Sự mở rộng nói chung của các sản phẩm ARM không thể được phân loại thành một số thông tin cụ thể. Nhưng các sản phẩm của ARM có thể được hiểu dựa trên kiến trúc của nó. Các bộ vi xử lý dòng ARM tiêu chuẩn hiện có trên thị trường bắt đầu từ ARM7 đến ARM11. Các bộ xử lý này có một số tính năng như bộ nhớ đệm, bộ nhớ Data Tightly Coupled, MPU, MMU, v.v. Một số dòng bộ xử lý ARM được biết đến rộng rãi là ARM926EJ-S, ARM7TDMI và ARM11 MPCore. Bài viết này đặc biệt dành cho tổng quan về kiến trúc vi điều khiển LPC2148 dựa trên ARM7 sẽ cung cấp cho bạn thông tin ngắn gọn về bộ vi điều khiển ngành kiến trúc.

Kiến trúc vi điều khiển LPC2148 dựa trên ARM7

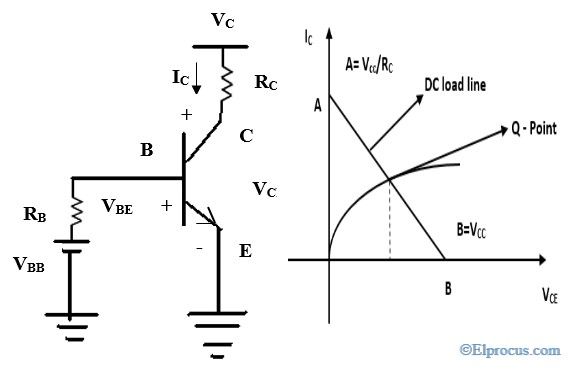

ARM7 là một mục đích chung 32 bit bộ vi xử lý và nó cung cấp một số tính năng như sử dụng ít điện năng và hiệu suất cao. Kiến trúc của một ARM phụ thuộc vào nguyên tắc của RISC . Cơ chế giải mã liên quan, cũng như tập lệnh RISC- rất dễ dàng khi chúng ta so sánh với CISC được lập trình vi mô -Complex Bộ hướng dẫn Máy tính.

Phương pháp Pipeline được sử dụng để xử lý tất cả các khối trong kiến trúc. Nói chung, một tập lệnh duy nhất đang được thực hiện, sau đó tập lệnh con của nó đang được dịch, & a 3rd-cấu trúc đang được lấy từ bộ nhớ.

Độc quyền kế hoạch kiến trúc của ARM7 được gọi là Ngón tay cái, và nó hoàn toàn thích hợp cho các ứng dụng có khối lượng lớn, nơi mà tính nhỏ gọn của mã là một vấn đề. ARM7 cũng sử dụng một kiến trúc độc quyền là Thumb. Nó làm cho nó hoàn toàn phù hợp cho các ứng dụng khác nhau bởi giới hạn bộ nhớ trong đó mật độ mã là một vấn đề.

Kiến trúc vi điều khiển dựa trên ARM7 (LPC2148)

Nguồn gián đoạn

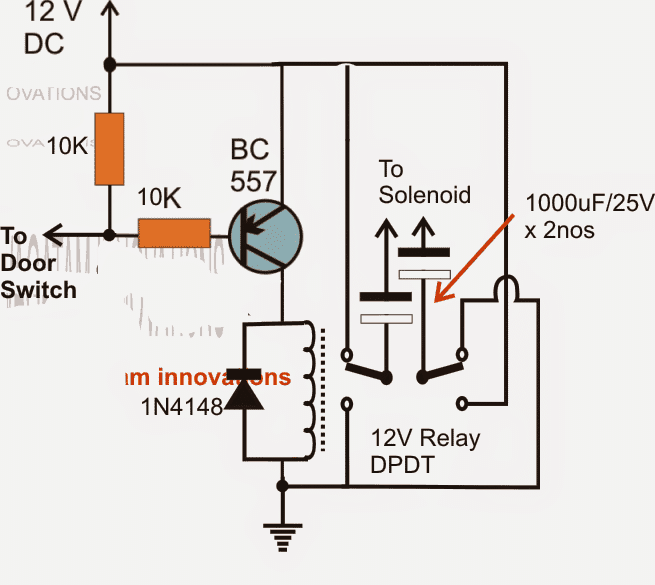

Mọi thiết bị ngoại vi bao gồm một đường ngắt duy nhất liên quan đến VIC (bộ điều khiển ngắt vector), mặc dù nó có thể có nhiều cờ ngắt bên trong. Các cờ ngắt riêng lẻ cũng có thể biểu thị một hoặc nhiều tài nguyên ngắt.

Bộ nhớ chương trình flash trên chip

Bộ vi điều khiển LPC2141 / 42/44/46/48 bao gồm một bộ nhớ flash tương ứng như 32-kilobyte, kilobyte, 128-kilobyte, 256-kilobyte. Bộ nhớ flash này có thể được sử dụng cho cả việc lưu trữ dữ liệu cũng như mã. Việc lập trình bộ nhớ flash có thể được thực hiện trong hệ thống thông qua cổng nối tiếp.

Ứng dụng chương trình cũng có thể xóa trong khi ứng dụng của chương trình đang chạy, cho phép tính linh hoạt của các cải tiến phần sụn trường lưu trữ dữ liệu, v.v. Do lựa chọn giải pháp kiến trúc cho bộ nạp khởi động trên chip, bộ nhớ khả dụng cho bộ vi điều khiển LPC2141 / 42 / 44/46/48 là 32-kilobyte, kilobyte, 128-kilobyte, 256-kilobyte và 500-kilobyte. Bộ nhớ flash của các bộ vi điều khiển này cung cấp 1, 00.000 lần xóa mỗi chu kỳ và bảo quản dữ liệu trong nhiều năm.

Pin Connect Block

Khối này cho phép các chân đã chọn của bộ vi điều khiển LPC2148 dựa trên ARM7 có một số chức năng. Bộ ghép kênh có thể được điều khiển bởi các thanh ghi cấu hình để cho phép liên kết giữa chân cắm cũng như các thiết bị ngoại vi trên chip.

Các thiết bị ngoại vi phải được ghép nối với các chân thích hợp trước khi được kích hoạt và trước khi cho phép bất kỳ ngắt được kết nối nào. Chức năng của bộ vi điều khiển có thể được xác định bởi mô-đun điều khiển chân bằng cách lựa chọn các thanh ghi của nó trong một môi trường phần cứng nhất định.

Sau khi sắp xếp lại tất cả các chân của các cổng (cổng 0 & cổng 1) được sắp xếp thành i / p bởi các ngoại lệ đã cho. Nếu cho phép gỡ lỗi

Nếu cho phép gỡ lỗi, các chân của JTAG sẽ đoán chức năng của JTAG. Nếu một dấu vết được cho phép, thì các chân Dấu vết sẽ đoán chức năng của dấu vết. Các chân kết nối với các chân I2C0 và I2C1 là chân mở.

GPIO- Mục đích chung Đầu vào / đầu ra song song

Thanh ghi GPIO điều khiển các chân thiết bị không được liên kết với một chức năng ngoại vi cụ thể. Các chân của thiết bị có thể được sắp xếp như i / p [s hoặc o / ps. Các sổ đăng ký riêng lẻ cho phép xóa đồng thời bất kỳ số lượng o / p nào. Giá trị thanh ghi đầu ra có thể được đọc lại và tình trạng hiện tại của các chân cổng. Các bộ vi điều khiển này bắt đầu một chức năng tăng tốc trên các thiết bị LPC200.

Các thanh ghi đầu vào / đầu ra có mục đích chung được chuyển đến bus bộ xử lý được sử dụng cho thời gian I / O có thể xảy ra tốt nhất.

- Các thanh ghi này là các byte địa chỉ.

- Tổng giá trị của một cổng có thể là

- Giá trị hoàn chỉnh của cổng có thể được viết trong lệnh duy nhất

10-bit ADC (Bộ chuyển đổi tương tự sang kỹ thuật số)

Các bộ vi điều khiển như LPC2141 hoặc 42 bao gồm hai Bộ chuyển đổi ADC và đây chỉ là 10-bit có một & LPC2144 / 46/48 có hai ADC và đây chỉ là ADC xấp xỉ thẳng 10-bit. Mặc dù ADC0 bao gồm 6 kênh và ADC1 có 8 kênh. Do đó, số lượng ADC i / ps có thể truy cập cho LPC2141 hoặc 42 là 6 & 14 cho LPC2141 hoặc 42.

DAC 10-bit (Bộ chuyển đổi kỹ thuật số sang tương tự)

DAC cho phép các vi điều khiển này tạo ra o / p tương tự có thể thay đổi, và VREFlà đầu ra tối đa của một kỹ thuật số sang tương tự Vôn.

Bộ điều khiển thiết bị-USB 2.0

Bus nối tiếp phổ biến bao gồm 4 dây và hỗ trợ giao tiếp giữa một số thiết bị ngoại vi và máy chủ. Bộ điều khiển này cho phép băng thông của USB để kết nối các thiết bị sử dụng giao thức dựa trên mã thông báo.

Xe buýt hỗ trợ rút phích cắm nóng và thu thập động của các thiết bị. Mọi giao tiếp được bắt đầu thông qua host-controller. Các bộ vi điều khiển này được thiết kế với bộ điều khiển bộ máy bus nối tiếp đa năng cho phép dữ liệu 12 Mbit / giây được thay thế bằng bộ điều khiển chủ của USB.

UART

Các bộ vi điều khiển này bao gồm hai UART để truyền và nhận đường dữ liệu tiêu chuẩn. Trái ngược với các bộ vi điều khiển trước đó (LPC2000), UART trong bộ vi điều khiển LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 khởi chạy bộ tạo tốc độ truyền một phần được sử dụng cho cả hai UART, cho phép các loại vi điều khiển này đạt được tốc độ truyền điển hình như 115200 bởi mọi tần số tinh thể trên 2 MHz . Ngoài ra, các chức năng điều khiển như CTS / RTS được thực thi hoàn toàn trong phần cứng.

Bộ điều khiển I / O nối tiếp của I2C-bus

Mỗi bộ vi điều khiển từ LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 bao gồm hai I2C bộ điều khiển xe buýt, và điều này là hai chiều. Việc điều khiển liên IC có thể được thực hiện với sự trợ giúp của hai dây dẫn là SCL và SDA. Ở đây SDA & SCL là dòng đồng hồ nối tiếp và dòng dữ liệu nối tiếp

Mọi bộ máy được xác định bởi một địa chỉ riêng. Ở đây, máy phát và máy thu có thể hoạt động ở hai chế độ như chế độ chủ / chế độ phụ. Đây là một bus đa master và nó có thể được quản lý bởi một hoặc nhiều bus master được liên kết với nó. Các bộ vi điều khiển này hỗ trợ tốc độ bit lên đến 400 kbit / s.

Bộ điều khiển đầu vào / đầu ra nối tiếp SPI

Các bộ vi điều khiển này bao gồm một bộ điều khiển SPI duy nhất và được thiết kế để xử lý nhiều phần mềm chính và phần tử được liên kết với một bus được chỉ định.

Đơn giản chỉ cần một master & một slave có thể trò chuyện trên giao diện trong suốt quá trình truyền dữ liệu được chỉ định. Trong quá trình này, master liên tục truyền một byte dữ liệu về phía phụ, cũng như slave liên tục truyền dữ liệu về phía chủ.

Bộ điều khiển đầu vào / đầu ra nối tiếp SSP

Các bộ vi điều khiển này chứa SSP đơn và bộ điều khiển này có khả năng xử lý trên SPI, bus Microwire hoặc SSI 4 dây. Nó có thể giao tiếp với xe buýt của một số chủ nhân cũng như nô lệ

Tuy nhiên, chỉ cần một master cụ thể, cũng như slave, có thể trò chuyện trên bus trong suốt quá trình truyền dữ liệu được chỉ định. Bộ vi điều khiển này hỗ trợ truyền song công, bởi các khung dữ liệu 4-16 bit được sử dụng cho luồng dữ liệu từ chủ - tớ cũng như từ tớ-chủ.

Bộ hẹn giờ / Bộ đếm

Bộ hẹn giờ và bộ đếm được thiết kế để đếm chu kỳ PCLK (đồng hồ ngoại vi) & tùy chọn tạo ra các ngắt dựa trên các thanh ghi 4 trận đấu.

Và nó bao gồm bốn i / ps bắt để bắt giá trị của bộ đếm thời gian khi tín hiệu i / p thay đổi. Một số chân có thể được chọn để thực hiện một chụp cụ thể. Các bộ vi điều khiển này có thể tính toán các sự kiện bên ngoài trên các đầu vào của quá trình bắt nếu xung bên ngoài nhỏ nhất là tương đương. Theo cách sắp xếp này, các dòng chụp nhàn rỗi có thể được chọn làm i / ps chụp hẹn giờ thông thường.

Bộ hẹn giờ cho cơ quan giám sát

Bộ đếm thời gian của cơ quan giám sát được sử dụng để thiết lập lại bộ vi điều khiển trong một khoảng thời gian hợp lý. Khi nó được cho phép thì bộ hẹn giờ sẽ tạo ra thiết lập lại hệ thống nếu chương trình tiêu dùng không thành công để tải lại bộ hẹn giờ trong một khoảng thời gian cố định.

RTC-Đồng hồ thời gian thực

RTC được thiết kế để cung cấp các bộ đếm để tính toán thời gian khi phương thức hoạt động nhàn rỗi hoặc bình thường được chọn. RTC sử dụng một lượng điện năng nhỏ và được thiết kế để bố trí phù hợp với nguồn năng lượng pin khi bộ xử lý trung tâm không hoạt động liên tục

Kiểm soát nguồn điện

Các bộ vi điều khiển này hỗ trợ hai chế độ năng lượng ngưng tụ như chế độ tắt nguồn và chế độ nhàn rỗi. Ở chế độ Chờ, việc thực thi các lệnh được cân bằng cho đến khi xảy ra ngắt hoặc RST. Các chức năng của thiết bị ngoại vi duy trì hoạt động trong suốt chế độ nhàn rỗi và có thể tạo ra các ngắt để khiến CPU khởi động lại quá trình hoàn thiện. Chế độ nhàn rỗi sẽ loại bỏ điện năng được sử dụng bởi CPU, bộ điều khiển, hệ thống bộ nhớ và các bus bên trong.

Ở chế độ tắt nguồn, bộ dao động bị vô hiệu hóa và IC không nhận được đồng hồ bên trong. Các thanh ghi ngoại vi, tình trạng bộ xử lý với các thanh ghi, giá trị SRAM bên trong được bảo toàn trong chế độ Power-down & các chân đầu ra mức logic của chip vẫn cố định.

Chế độ này có thể được kết thúc và quá trình chung được khởi động lại bằng các ngắt cụ thể có khả năng hoạt động mà không cần đồng hồ. Bởi vì hoạt động của chip được cân bằng, chế độ Power-down sẽ giảm mức sử dụng năng lượng của chip xuống gần như bằng không.

PWM -Pulse Width Modulator

Các PWM dựa trên khối bộ định thời bình thường và cũng có tất cả các tính năng, mặc dù chỉ đơn giản là chức năng điều chế độ rộng xung được cố định trên các bộ vi điều khiển như LPC2141 / 42/44/46/48.

Bộ định thời nhằm tính toán chu kỳ PCLK (đồng hồ ngoại vi) & tùy chọn tạo ra các ngắt khi các giá trị bộ định thời cụ thể phát sinh dựa trên các thanh ghi 7 khớp và chức năng PWM cũng phụ thuộc vào các sự kiện đăng ký khớp.

Khả năng điều khiển riêng lẻ các vị trí biên tăng và giảm cho phép sử dụng điều chế độ rộng xung cho một số ứng dụng. Ví dụ, điều khiển động cơ điển hình với nhiều pha sử dụng 3 đầu ra không chồng chéo của PWM bằng cách điều khiển riêng biệt mọi độ rộng xung cũng như các vị trí.

Xe buýt VPB

Bộ chia VPB giải quyết mối liên hệ giữa CCLK (đồng hồ bộ xử lý) và PCLK (đồng hồ được sử dụng bởi các thiết bị ngoại vi). Dải phân cách này được sử dụng cho hai mục đích. Việc sử dụng đầu tiên là cung cấp thiết bị ngoại vi bởi PCLK ưu tiên sử dụng bus VPB để chúng có thể hoạt động ở tốc độ đã chọn của bộ xử lý ARM. Để thực hiện điều này, tốc độ bus này có thể được giảm tốc độ xung nhịp của bộ xử lý từ 1⁄ 2 -1⁄ 4.

Bởi vì bus này phải hoạt động chính xác khi bật nguồn và trạng thái mặc định lúc RST (đặt lại) là bus hoạt động ở 1/4 tốc độ xung nhịp của bộ xử lý. Công dụng thứ hai của điều này là cho phép tiết kiệm năng lượng bất cứ khi nào ứng dụng không cần bất kỳ thiết bị ngoại vi nào để hoạt động ở tốc độ bộ xử lý hoàn chỉnh. Vì bộ chia VPB được liên kết với đầu ra của PLL, bộ chia này vẫn hoạt động trong suốt chế độ nhàn rỗi.

Mô phỏng & gỡ lỗi

Bộ vi điều khiển (LPC2141 / 42/44/46/48) tổ chức mô phỏng và gỡ lỗi thông qua cổng nối tiếp-JTAG. Một cho phép cổng theo dõi theo dõi việc thực thi chương trình. Các chức năng theo dõi và các khái niệm gỡ lỗi được ghép với port1 và GPIO.

Bảo mật mã

Tính năng bảo mật mã của các bộ vi điều khiển LPC2141 / 42/44/46/48 này cho phép một chức năng kiểm soát xem nó có thể được bảo vệ hoặc gỡ lỗi khi kiểm tra hay không.

Vì vậy, đây là tất cả về kiến trúc vi điều khiển LPC2148 dựa trên ARM7. Từ bài báo trên, cuối cùng, chúng ta có thể kết luận rằng ARM là một kiến trúc được sử dụng trong nhiều bộ vi xử lý cũng như vi điều khiển. Đây là một câu hỏi dành cho bạn, kiến trúc của bộ xử lý ARM là gì?