Trong cuộc sống hàng ngày, chúng ta bắt gặp nhiều loại thiết bị điện tử khác nhau. Một trong những công nghệ đã tạo ra một cuộc cách mạng trong sản xuất điện tử là “ Mạch tích hợp “. Công nghệ này làm giảm kích thước của các sản phẩm điện tử bằng cách tăng mật độ cổng logic mỗi chip. Ngày nay chúng ta có các loại và cấu hình khác nhau của IC. Khi quan sát xung quanh, chúng tôi thấy rằng một số IC chỉ có thể được sử dụng cho một ứng dụng cụ thể trong khi một số IC có thể được lập trình lại và sử dụng cho các ứng dụng khác nhau. Các loại IC này được đặt tên là ASIC. Nhưng chúng khác nhau như thế nào? Làm thế nào có thể lập trình lại chúng? Tại sao một số IC không thể được lập trình lại? Hy vọng sẽ tìm thấy câu trả lời cho những câu hỏi này.

ASIC (Mạch tích hợp ứng dụng cụ thể) là gì?

ASIC dạng đầy đủ là Mạch tích hợp ứng dụng cụ thể. Các mạch này là ứng dụng cụ thể. I.e. IC được thiết kế riêng cho một ứng dụng cụ thể. Chúng thường được thiết kế từ cấp gốc dựa trên yêu cầu của ứng dụng cụ thể. Một số điều cơ bản ví dụ về mạch tích hợp ứng dụng cụ thể là chip được sử dụng trong đồ chơi, chip được sử dụng để giao tiếp bộ nhớ và bộ vi xử lý, v.v… Những chip này chỉ có thể được sử dụng cho một ứng dụng mà chúng được thiết kế. Có lẽ, những các loại IC chỉ được ưu tiên cho những sản phẩm có quy trình sản xuất lớn. Vì ASIC được thiết kế từ cấp cơ sở nên chúng có giá thành cao và chỉ được khuyến nghị cho các sản phẩm số lượng lớn.

Ưu điểm chính của ASIC là giảm kích thước chip do một số lượng lớn các đơn vị chức năng của mạch được xây dựng trên một chip duy nhất. ASIC hiện đại thường bao gồm 32-bit bộ vi xử lý , khối bộ nhớ, mạch mạng, v.v.… Loại ASIC như vậy được gọi là Hệ thống trên chip . Với sự phát triển trong công nghệ sản xuất và tăng cường nghiên cứu các phương pháp thiết kế, các ASIC với các mức độ tùy biến khác nhau được phát triển.

Các loại ASIC

ASIC được phân loại dựa trên số lượng tùy chỉnh mà một lập trình viên được phép thực hiện trên một con chip.

Các loại ASIC

Hoàn toàn tùy chỉnh

Trong kiểu thiết kế này, tất cả các ô logic được thiết kế riêng cho các ứng dụng cụ thể. I.e. nhà thiết kế phải đặc biệt tạo ra các ô logic cho các mạch. Tất cả các lớp mặt nạ để kết nối với nhau đều được tùy chỉnh. Vì vậy, lập trình viên không thể thay đổi các kết nối của chip và trong khi lập trình, anh ta phải lưu ý về cách bố trí mạch.

Một trong những ví dụ tốt nhất về ASIC hoàn toàn tùy chỉnh là một bộ vi xử lý. Loại tùy chỉnh này cho phép các nhà thiết kế xây dựng các mạch tương tự khác nhau, các ô nhớ được tối ưu hóa hoặc cấu trúc cơ học trên một vi mạch duy nhất. ASIC này rất tốn kém và tốn rất nhiều thời gian để sản xuất và thiết kế. Thời gian để thiết kế các vi mạch này là khoảng tám tuần.

Chúng thường dành cho các ứng dụng cấp cao. Hiệu suất tối đa, diện tích giảm thiểu và mức độ linh hoạt cao nhất là những đặc điểm chính của thiết kế Full custom. Cuối cùng, rủi ro cao trong thiết kế vì các tế bào logic, điện trở, v.v. các phần tử mạch được sử dụng không được kiểm tra trước.

Bán tùy chỉnh

Trong kiểu thiết kế này, các ô logic được lấy từ các thư viện tiêu chuẩn. I.e. chúng không được làm thủ công như trong thiết kế hoàn toàn tùy chỉnh. Một số mặt nạ được tùy chỉnh trong khi một số được lấy từ thư viện được thiết kế trước. Dựa trên loại ô logic được lấy từ thư viện và số lượng tùy chỉnh được phép kết nối với nhau, các ASIC này được chia thành hai loại - ASIC dựa trên ô tiêu chuẩn và ASIC dựa trên mảng cổng.

1). ASIC dựa trên tế bào tiêu chuẩn

Để biết các vi mạch này trước tiên chúng ta hãy hiểu thư viện ô tiêu chuẩn là viết tắt của gì. Một số ô logic như Cổng VÀ, cổng HOẶC , bộ ghép kênh, dép tông được thiết kế trước bởi các nhà thiết kế bằng cách sử dụng các cấu hình khác nhau, được tiêu chuẩn hóa và lưu trữ dưới dạng thư viện. Bộ sưu tập này được gọi là thư viện ô tiêu chuẩn.

ASIC dựa trên tế bào tiêu chuẩn

Trong tiêu chuẩn dựa trên ô, ô logic ASIC từ các thư viện tiêu chuẩn này được sử dụng. Trên vùng ô tiêu chuẩn của chip ASIC hoặc khối linh hoạt được tạo thành từ các ô tiêu chuẩn được sắp xếp dưới dạng hàng. Cùng với các khối linh hoạt này, các tế bào mega như vi điều khiển hoặc thậm chí vi xử lý được sử dụng trên chip. Các ô mega này còn được gọi là hàm Mega, macro cấp hệ thống, khối cố định, Khối tiêu chuẩn chức năng.

Hình trên đại diện cho một ô tiêu chuẩn ASIC với một vùng ô tiêu chuẩn duy nhất và bốn khối cố định. Các lớp mặt nạ được tùy chỉnh. Ở đây nhà thiết kế có thể đặt các ô tiêu chuẩn ở bất cứ đâu trên khuôn. Chúng còn được gọi là C-BIC.

2). Cổng ASIC dựa trên mảng cổng

Loại ASIC bán tùy chỉnh này đã được xác định trước Linh kiện bán dẫn trên tấm silicon .i.e. nhà thiết kế không thể thay đổi vị trí của các bóng bán dẫn có trên khuôn. Mảng cơ sở là mẫu được xác định trước của mảng cổng và ô cơ sở là ô lặp lại nhỏ nhất của mảng cơ sở.

Nhà thiết kế chỉ có trách nhiệm thay đổi kết nối giữa các bóng bán dẫn bằng cách sử dụng một vài lớp kim loại đầu tiên của khuôn. Người thiết kế chọn từ thư viện mảng cổng. Chúng thường được gọi là Mảng cổng có mặt nạ. Cổng ASIC dựa trên mảng cổng có ba loại. Đó là Mảng cổng phân luồng, Mảng cổng ít kênh và mảng cổng có cấu trúc.

a) Mảng cổng .hanneled

Trong loại mảng cổng này, không gian đi dây được để lại giữa các hàng bóng bán dẫn. Chúng tương tự như CBIC vì không gian được để lại cho sự kết nối giữa các khối nhưng trong các dãy ô cổng có kênh được cố định về chiều cao trong khi trong CBIC, không gian này có thể được điều chỉnh.

Mảng cổng phân luồng

Một số tính năng chính của mảng cổng này là - mảng cổng này sử dụng các khoảng trống được xác định trước giữa các hàng để kết nối với nhau. Thời gian sản xuất là hai ngày đến hai tuần.

b). Mảng ít cổng hơn

Không còn không gian trống để định tuyến giữa các hàng ô như được thấy trong mảng cổng được phân kênh. Ở đây việc định tuyến được thực hiện từ phía trên các ô cổng vì chúng ta có thể tùy chỉnh kết nối giữa kim loại 1 và các bóng bán dẫn. Đối với định tuyến, chúng tôi để các bóng bán dẫn nằm trong đường dẫn định tuyến không sử dụng. Thời gian dẫn đầu sản xuất là khoảng hai tuần.

Mảng ít cổng hơn

c). Mảng cổng có cấu trúc

Loại mảng cổng này có một khối nhúng cùng với các hàng mảng cổng như đã thấy ở trên. Mảng cổng có cấu trúc có hiệu suất diện tích cao hơn CBIC. Giống như mảng cổng có mặt nạ, chúng có chi phí thấp hơn và quay vòng nhanh hơn. Ở đây kích thước cố định của hàm nhúng đặt ra một hạn chế đối với mảng cổng có cấu trúc. Ví dụ: mảng cổng này có chứa một khu vực dành riêng cho bộ điều khiển 32k bit nhưng nếu trong một ứng dụng chúng ta chỉ yêu cầu một khu vực cho bộ điều khiển 16k bit thì khu vực còn lại sẽ bị lãng phí. Tất cả mảng cổng có thời gian quay vòng từ hai ngày đến hai tuần và tất cả đều có kết nối tùy chỉnh.

Mảng cổng có cấu trúc

ASIC có thể lập trình

Có hai loại ASIC có thể lập trình. Chúng là PLD và FPGA

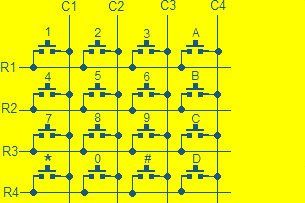

PLDs (Thiết bị logic có thể lập trình)

Đây là những ô tiêu chuẩn có sẵn. Chúng tôi có thể lập trình PLD để tùy chỉnh một phần của ứng dụng, vì vậy chúng được coi là ASIC. Chúng ta có thể sử dụng các phương pháp và phần mềm khác nhau để lập trình PLD. Chúng chứa một ma trận thông thường gồm các ô logic thường là logic mảng có thể lập trình được cùng với các ô lật hoặc chốt. Ở đây các kết nối hiện diện như một khối lớn duy nhất.

PROM là một ví dụ phổ biến của vi mạch này. EPROM sử dụng các bóng bán dẫn MOS làm kết nối với nhau nên bằng cách áp dụng điện áp cao, chúng tôi có thể lập trình nó. PLD không có ô logic tùy chỉnh hoặc kết nối với nhau. Chúng có sự thay đổi thiết kế nhanh chóng.

Thiết bị logic có thể lập trình

FPGA (Mảng cổng lập trình trường)

Trong đó PLD có lôgic mảng có thể lập trình dưới dạng các ô logic FPGA có sự sắp xếp giống như mảng cổng. PLD nhỏ hơn và ít phức tạp hơn FPGA. Do tính linh hoạt và đặc điểm của nó, FPGA đang thay thế TTL trong hệ thống vi điện tử. Vòng quay thiết kế chỉ mất vài giờ.

Mảng cổng lập trình trường

Phần lõi bao gồm các ô logic cơ bản có thể lập trình được có thể thực hiện cả hai tổ hợp và logic tuần tự . Chúng ta có thể lập trình các ô logic và kết nối với nhau bằng một số phương pháp. Các ô logic cơ bản được bao quanh bởi ma trận các kết nối có thể lập trình được và lõi được bao quanh bởi các ô I / O có thể lập trình.

FPGA thường bao gồm các khối logic có thể định cấu hình, các khối I / O có thể định cấu hình, các kết nối có thể lập trình được, mạch đồng hồ, ALU, bộ nhớ, bộ giải mã.

Chúng tôi đã thấy các loại ASIC khác nhau có sẵn. Bây giờ, hãy hiểu khi nào tất cả các tùy chỉnh và kết nối này được thực hiện trong quá trình sản xuất.

Quy trình thiết kế mạch tích hợp cụ thể cho ứng dụng (ASIC)

Việc thiết kế một ASIC được thực hiện theo từng bước. Thứ tự các bước này được gọi là Thiết kế ASIC Lưu lượng. Các bước của quy trình thiết kế được đưa ra trong biểu đồ bên dưới.

Quy trình thiết kế ASIC

Đầu vào thiết kế: Ở bước này, vi kiến trúc của thiết kế được thực hiện bằng các ngôn ngữ mô tả phần cứng như VHDL, Verilog và System Verilog.

Tổng hợp logic: Ở bước này, một danh sách ròng các ô logic sẽ được sử dụng, các loại kết nối và tất cả các phần khác cần thiết cho ứng dụng được chuẩn bị bằng HDL.

Phân vùng hệ thống: Ở bước này, chúng tôi chia khuôn có kích thước lớn thành các phần có kích thước ASIC.

Mô phỏng trước bố cục: Ở bước này, một bài kiểm tra mô phỏng được thực hiện để kiểm tra xem thiết kế có bất kỳ lỗi nào không.

Quy hoạch sàn: Tại bước này, các khối netlist được sắp xếp trên chip.

Vị trí: Tại bước này, vị trí của các ô bên trong khối được quyết định.

Định tuyến: Tại bước này, các kết nối được vẽ giữa các khối và ô. Trích xuất: Ở bước này, chúng tôi xác định các đặc tính điện như giá trị điện trở và giá trị điện dung của kết nối.

Mô phỏng sau bố cục: Trước khi gửi mô hình để sản xuất mô phỏng này được thực hiện để kiểm tra xem hệ thống có hoạt động bình thường hay không cùng với tải kết nối.

Ví dụ về ASIC

Đã biết các đặc điểm khác nhau của ASIC, bây giờ chúng ta hãy xem một số ví dụ về ASIC.

ASIC dựa trên tế bào tiêu chuẩn: LCB 300k, 500k từ LSI Logic Company, SIG1, 2, 3 family từ ABB Hafo Inc., GCS90K của GCS Plessey.

Sản phẩm mảng cổng: AUA20K từ Harris Semiconductor, SCX6Bxx từ National Semiconductors, TGC / TEC từ Texas Instruments.

Sản phẩm PLD: Dòng PAL gồm các Thiết bị Micro nâng cao, dòng GAL từ Philips Semiconductors, XC7300 và EPLD từ XILINX.

Sản phẩm FPGA: Dòng XC2000, XC3000, XC4000, XC5000 của XILINX, pASIC1 của QuickLogic, MAX5000 của Altera.

Các ứng dụng của ASIC

Tính độc đáo của ASIC đã cách mạng hóa cách sản xuất thiết bị điện tử. Những điều này làm giảm kích thước khuôn trong khi tăng mật độ cổng logic mỗi chip. ASIC thường được ưu tiên cho các ứng dụng cấp cao. Chip ASIC được sử dụng làm lõi IP cho vệ tinh, sản xuất ROM, Vi điều khiển và các loại ứng dụng khác nhau trong lĩnh vực y tế và nghiên cứu. Một trong những ứng dụng thịnh hành của ASIC là BITCOIN MINER.

Thợ mỏ Bitcoin

Khai thác tiền điện tử đòi hỏi sức mạnh lớn hơn và phần cứng tốc độ cao. Một CPU đa năng không thể cung cấp khả năng tính toán cao hơn ở tốc độ cao. Máy khai thác bitcoin ASIC là những con chip được tích hợp trong bo mạch chủ được thiết kế đặc biệt và nguồn điện , được xây dựng thành một đơn vị duy nhất. Nó là một phần cứng được thiết kế có chủ đích ở cấp độ chip để khai thác bitcoin. Các đơn vị này chỉ có thể thực thi thuật toán của một loại tiền điện tử duy nhất. Có lẽ đối với một loại tiền điện tử khác, chúng tôi yêu cầu một công cụ khai thác khác.

Ưu điểm & Nhược điểm của ASIC

Các lợi thế của ASIC bao gồm những điều sau đây.

- Kích thước nhỏ của ASIC làm cho nó trở thành một lựa chọn cao cho các hệ thống lớn hơn phức tạp.

- Vì một số lượng lớn các mạch được xây dựng trên một chip duy nhất, điều này gây ra các ứng dụng tốc độ cao.

- ASIC có mức tiêu thụ điện năng thấp.

- Vì chúng là hệ thống trên chip, các mạch hiện diện cạnh nhau. Vì vậy, cần định tuyến rất tối thiểu để kết nối các mạch khác nhau.

- ASIC không có vấn đề về thời gian và cấu hình hậu sản xuất.

Các nhược điểm của ASIC bao gồm những điều sau đây.

- Vì đây là những con chip tùy chỉnh nên chúng cung cấp tính linh hoạt thấp cho việc lập trình.

- Vì các chip này phải được thiết kế từ cấp cơ sở nên chúng có giá thành cao trên mỗi đơn vị.

- ASIC có thời gian ký quỹ thị trường lớn hơn.

ASIC và FPGA

Sự khác biệt giữa ASIC và FPGA bao gồm những điều sau đây.

ASIC | FPGA |

| Không thể lập trình lại | Có thể lập trình lại |

| Được ưu tiên cho các sản phẩm số lượng lớn | Được ưu tiên cho các sản phẩm số lượng ít |

| Đây là những ứng dụng cụ thể | Được sử dụng làm nguyên mẫu của một hệ thống |

| Tiết kiệm năng lượng yêu cầu ít điện năng hơn | Tiết kiệm năng lượng hơn đòi hỏi nhiều năng lượng hơn |

| Đây là những mạch điện vĩnh viễn không thể được nâng cấp theo thời gian. | Rất thích hợp cho các ứng dụng mà mạch phải được nâng cấp theo thời gian như chip điện thoại di động, trạm gốc, v.v. |

Vì vậy, đây là tất cả về tổng quan về Mạch tích hợp ứng dụng cụ thể . Việc phát minh ra ASIC đã tạo ra một sự thay đổi to lớn trong cách sử dụng thiết bị điện tử. Chúng tôi sử dụng ASIC trong cuộc sống hàng ngày của chúng tôi dưới dạng các ứng dụng khác nhau. Bạn đã xem qua những ứng dụng nào của ASIC? Bạn đã làm việc với loại ASIC nào?