Trên thực tế, không thể kết nối trực tiếp các thiết bị I/O với bus dữ liệu của bộ xử lý. Vì vậy, ở vị trí của nó, phải có một số thiết bị có cổng I/O để kết nối các thiết bị I/O như 8255 bộ vi xử lý . Bộ xử lý này thuộc họ MCS-85 do Intel thiết kế và nó có thể được sử dụng với 8086 & bộ vi xử lý 8085 . 8255 là một thiết bị giao diện ngoại vi có thể lập trình được sử dụng để đạt được phương thức giao tiếp cơ bản giữa bộ vi xử lý và máy móc. Nó là một thiết bị ngoại vi được sử dụng cho một máy được lập trình để hoạt động như một giao diện. 8255 PPI này là giao diện giữa bộ vi xử lý và thiết bị I/O. Bài viết này thảo luận về một cái nhìn tổng quan về một Bộ vi xử lý 8255 - làm việc với các ứng dụng.

Bộ vi xử lý 8255 là gì?

Bộ vi xử lý 8255 là chip giao diện ngoại vi có thể lập trình hoặc chip PPI được sử dụng rất phổ biến. Chức năng của bộ vi xử lý 8255 là truyền dữ liệu trong các điều kiện khác nhau từ I/O đơn giản đến I/O ngắt. Bộ vi xử lý này cũng được thiết kế để kết nối CPU với thế giới bên ngoài của nó như ADC , bàn phím, DAC, v.v. Bộ vi xử lý này tiết kiệm, có nhiều chức năng và linh hoạt mặc dù hơi phức tạp, vì vậy nó có thể được sử dụng với bất kỳ bộ vi xử lý nào. Bộ vi xử lý này được sử dụng để kết nối các thiết bị ngoại vi và cũng để giao tiếp. Vì vậy thiết bị ngoại vi này còn được gọi là thiết bị I/O vì các cổng I/O của bộ vi xử lý này được sử dụng để kết nối các thiết bị I/O. Bộ xử lý này bao gồm ba cổng I/O hai chiều 8-bit có thể được cấu hình khi cần thiết.

Đặc trưng

Các Đặc điểm của bộ vi xử lý 8255 bao gồm những điều sau đây.

- Bộ vi xử lý 8255 là một thiết bị PPI (giao diện ngoại vi có thể lập trình).

- Nó bao gồm ba cổng I/O được lập trình trong các chế độ khác nhau.

- Bộ vi xử lý này chỉ cung cấp một số phương tiện để kết nối các thiết bị khác nhau. Do đó, nó được sử dụng trong các ứng dụng khác nhau thường xuyên.

- Nó hoạt động ở ba chế độ như Chế độ 0 (I/O đơn giản), Chế độ 1 (I/O nhấp nháy) và Chế độ 2 (I/O hai chiều nhấp nháy).

- Nó hoàn toàn tương thích với các dòng vi xử lý của Intel.

- Nó tương thích với TTL.

- Đối với cổng-C của bộ vi xử lý này, khả năng SET/RESET bit trực tiếp khả dụng.

- Nó bao gồm 24 chân đầu vào/đầu ra có thể lập trình được đặt dưới dạng cổng 2 đến 8 bit và cổng 2 đến 4 bit.

- Nó bao gồm ba cổng 8 bit; Cổng-A, Cổng-B & Cổng-C.

- Ba cổng I/O bao gồm một thanh ghi điều khiển xác định chức năng của từng cổng I/O và chúng phải hoạt động ở chế độ nào.

Cấu hình chân bộ vi xử lý 8255

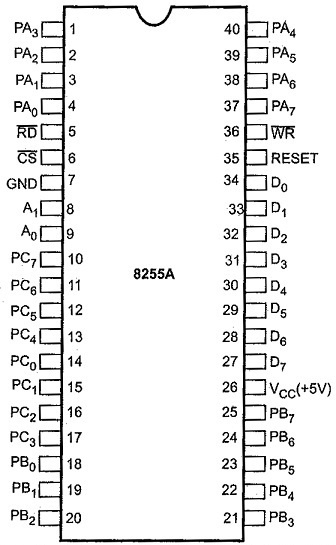

Sơ đồ chân của bộ vi xử lý 8255 được hiển thị bên dưới. Bộ vi xử lý này bao gồm 40 chân như PA7-PA0, PC7-PC0, PC3-PC0, PB0-PB7, RD, WR, CS, A1 & A0,D0-D7 và RESET. Những chân này được thảo luận dưới đây.

PA7 đến PA0 (Chân PortA)

PA7 đến PA0 là các chân đường dữ liệu của Cổng A (1 đến 4 & 37 đến 40) được phân bố đều trên hai mặt của mặt trên của bộ vi xử lý. Tám chân cổng A này hoạt động như các dòng đầu vào được đệm hoặc đầu ra được chốt dựa trên từ điều khiển được tải vào thanh ghi từ điều khiển.

PB0 đến PB7 (Chân Cổng B)

PB0 đến PB7 từ 18 đến 25 là các chân đường dữ liệu mang dữ liệu cổng B.

PC0 đến PC7 (Chân Cổng C)

Các chân PC0 đến PC7 là các chân của cổng C bao gồm chân 10 đến chân 17 mang các bit dữ liệu của cổng A. Từ đó, chân 10 – chân 13 được gọi là chân trên của Cổng C và chân từ chân 14 đến chân 17 được gọi là chân dưới. Các chân từ hai phần này có thể được sử dụng riêng lẻ để truyền 4 bit dữ liệu bằng hai phần cổng C riêng biệt.

D0 đến D7 (Chân bus dữ liệu)

Các chân D0 đến D7 này là các đường I/O dữ liệu bao gồm 27 chân đến 34 chân. Các chân này được sử dụng để mang mã nhị phân 8 bit và nó được sử dụng để huấn luyện toàn bộ hoạt động của vi mạch. Các chân này được gọi chung là thanh ghi điều khiển/từ điều khiển mang dữ liệu của từ điều khiển.

A0 & A1

Các chân A0 và A1 tại chân 8 & chân 9 chỉ cần đưa ra quyết định về cổng nào sẽ được ưu tiên để truyền dữ liệu.

Nếu A0 = 0 & A1=0 thì Port-A được chọn.

Nếu A0 = 0 & A1=1 thì Port-B được chọn.

Nếu A0 = 1 & A1 = 0 thì Port-C được chọn.

Nếu A0 = 1 & A1 = 1 thì thanh ghi điều khiển được chọn.

CS’

Chân 6 giống như CS’ là chân đầu vào chọn chip chịu trách nhiệm chọn chip. Tín hiệu thấp ở chân CS chỉ đơn giản là cho phép giao tiếp giữa 8255 và bộ xử lý, điều đó có nghĩa là ở chân này, hoạt động truyền dữ liệu được cho phép bởi tín hiệu thấp đang hoạt động.

RD'

Chân 5 giống như RD’ là chân đầu vào đọc đặt chip ở chế độ đọc. Tín hiệu thấp ở chân RD này cung cấp dữ liệu cho CPU bằng bộ đệm dữ liệu.

WR’

Chân 36 giống như chân WR’ là chân đầu vào ghi đặt chip ở chế độ ghi. Vì vậy, một tín hiệu thấp ở chân WR’ chỉ đơn giản cho phép CPU thực hiện thao tác ghi phía trên các cổng nếu không thanh ghi điều khiển của bộ vi xử lý thông qua bộ đệm bus dữ liệu.

CÀI LẠI

Pin35 giống như chân RESET đặt lại toàn bộ dữ liệu có sẵn trong tất cả các phím về giá trị mặc định của chúng khi ở chế độ cài đặt. Đó là một tín hiệu cao tích cực trong đó tín hiệu cao ở chân RESET sẽ xóa các thanh ghi điều khiển và các cổng được đặt trong chế độ đầu vào.

GND

Pin7 là chân GND của IC.

VCC

Chân 26 như VCC là chân đầu vào 5V của IC.

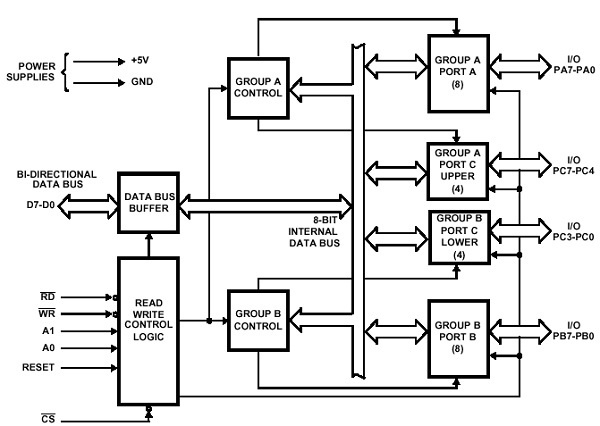

Kiến trúc bộ vi xử lý 8255

Kiến trúc của bộ vi xử lý 8255 được hiển thị bên dưới.

8255 Kiến trúc

Bộ đệm xe buýt dữ liệu:

Bộ đệm bus dữ liệu chủ yếu được sử dụng để kết nối bus bên trong của bộ vi xử lý với bus hệ thống để có thể thiết lập giao diện phù hợp giữa hai bus này. Bộ đệm này đơn giản cho phép thao tác đọc hoặc ghi được thực thi từ hoặc tới CPU. Bộ đệm này cho phép dữ liệu được cung cấp từ thanh ghi điều khiển hoặc các cổng tới CPU trong trường hợp thao tác ghi & từ CPU tới thanh ghi trạng thái hoặc các cổng trong trường hợp thao tác đọc.

Logic điều khiển đọc/ghi:

Đơn vị logic điều khiển đọc hoặc ghi điều khiển các hoạt động bên trong hệ thống. Đơn vị này có khả năng quản lý cả việc truyền dữ liệu & trạng thái hoặc các từ điều khiển bên trong và bên ngoài. Khi có dữ liệu cần tìm nạp thì nó cho phép địa chỉ được cung cấp bởi 8255 bằng bus & tạo lệnh ngay lập tức cho hai nhóm điều khiển cho hoạt động cụ thể.

Kiểm soát nhóm A & nhóm B:

Cả hai nhóm này đều do CPU quản lý và hoạt động dựa trên lệnh do CPU tạo ra. CPU này truyền các từ điều khiển tới hai nhóm này và chúng liên tiếp truyền lệnh phù hợp tới cổng cụ thể của chúng. Nhóm A điều khiển cổng A với các bit cổng C bậc cao hơn trong khi nhóm B điều khiển cổng B với các bit cổng C bậc thấp hơn.

Cổng A & Cổng B

Cổng A & Cổng B bao gồm chốt đầu vào 8 bit và đầu ra được đệm hoặc chốt 8 bit. Chức năng chính của các cổng này cũng không phụ thuộc vào phương thức hoạt động. Cổng A có thể được lập trình ở 3 chế độ như chế độ 0, 1 và 2 trong khi Cổng B có thể được lập trình ở chế độ 0 & chế độ 1.

Cảng C

Cổng C bao gồm bộ đệm đầu vào dữ liệu 8 bit và bộ đệm o/p dữ liệu hai chiều 8 bit. Cổng này chủ yếu được chia thành hai phần – cổng C PCU phía trên & cổng C PC phía dưới. Vì vậy hai phần này chủ yếu được lập trình & sử dụng riêng biệt như một cổng I/O 4 bit. Cổng này được sử dụng cho tín hiệu bắt tay, đầu vào tín hiệu trạng thái và I/O đơn giản. Cổng này được sử dụng kết hợp với cổng A & Cổng B cho cả tín hiệu trạng thái và bắt tay. Cổng này chỉ cung cấp dung lượng trực tiếp nhưng đặt hoặc đặt lại.

Chế độ hoạt động của bộ vi xử lý 8255

Bộ vi xử lý 8255 có hai chế độ hoạt động như chế độ thiết lập lại bit và chế độ đầu vào/đầu ra sẽ được thảo luận bên dưới.

Chế độ đặt lại bit

Chế độ thiết lập-đặt lại bit chủ yếu được sử dụng để chỉ đặt/đặt lại các bit Port-C. Trong loại chế độ hoạt động này, nó chỉ ảnh hưởng đến một bit thời gian của Cổng C. Sau khi người dùng đặt bit, thì nó sẽ tiếp tục được đặt cho đến khi nó không được người dùng đặt. Người dùng yêu cầu tải mẫu bit trong thanh ghi điều khiển để sửa đổi bit. Khi cổng C được sử dụng cho hoạt động điều khiển/trạng thái, thì bằng cách gửi lệnh OUT, mỗi bit cổng C riêng lẻ có thể được đặt/đặt lại.

Chế độ vào/ra

Chế độ I/O có ba chế độ khác nhau như Chế độ 0, Chế độ 1 & Chế độ 2 trong đó mỗi chế độ được thảo luận bên dưới.

Chế độ 0:

Đây là chế độ I/O của 8255 đơn giản cho phép lập trình từng cổng như cổng i/p hoặc cổng o/p. Vì vậy, tính năng I/O của chế độ này chỉ đơn giản bao gồm:

- Các cổng i/p được lưu vào bộ đệm bất cứ khi nào o/ps được chốt.

- Nó không hỗ trợ khả năng ngắt/bắt tay.

Chế độ 1:

Chế độ 1 của 8255 là I/O có bắt tay, vì vậy trong loại chế độ này, cả hai cổng như Cổng A & Cổng B đều được sử dụng làm cổng I/O trong khi cổng C được sử dụng để bắt tay. Vì vậy, chế độ này hỗ trợ bắt tay bởi các cổng được lập trình ở chế độ i/p hoặc o/p. Tín hiệu bắt tay chủ yếu được sử dụng để đồng bộ hóa việc truyền dữ liệu giữa hai thiết bị hoạt động ở các tốc độ khác nhau. Các đầu vào & đầu ra ở chế độ này được chốt và chế độ này cũng có khả năng ngắt xử lý & điều khiển tín hiệu để phù hợp với tốc độ của CPU & thiết bị IO.

Chế độ 2:

Mode2 là cổng I/O hai chiều có bắt tay. Vì vậy, các cổng trong loại chế độ này có thể được sử dụng cho luồng dữ liệu hai chiều thông qua các tín hiệu bắt tay. Các chân nhóm A có thể được lập trình để thực hiện như bus dữ liệu hai chiều & PC7 – PC4 ở cổng C được sử dụng thông qua tín hiệu bắt tay. Các bit cổng C thấp hơn còn lại được sử dụng cho các hoạt động đầu vào/đầu ra. Chế độ này có khả năng xử lý ngắt.

Bộ vi xử lý 8255 đang hoạt động

Bộ vi xử lý 8255 là một thiết bị I/O có thể lập trình cho mục đích chung được thiết kế chủ yếu để truyền dữ liệu từ I/O sang I/O ngắt trong một số điều kiện khi cần thiết. Điều này có thể được sử dụng gần như với bất kỳ bộ vi xử lý nào. Bộ vi xử lý này bao gồm 3 cổng I/O hai chiều 8 bit có thể được sắp xếp theo yêu cầu như PORT A, PORT B & PORT C. PPI 8255 này được thiết kế chủ yếu để giao tiếp giữa CPU với thế giới bên ngoài như bàn phím, ADC, DAC, v.v... Bộ vi xử lý này có thể được lập trình dựa trên một điều kiện cụ thể.

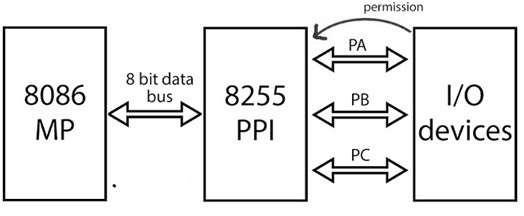

Giao tiếp 8255 PPI với 8086

Nhu cầu kết nối 8255 PPI với bộ vi xử lý 8086 là; bộ vi xử lý 8086 kích hoạt chân RD đầu vào của 8255 khi nó cần đọc dữ liệu có sẵn trong một cổng 8255. Đối với 8255, nó là chân i/p thấp đang hoạt động. Chân này được kết nối với WR o/p của bộ vi xử lý 8086. Bộ vi xử lý 8086 kích hoạt WR i/p của 8255 khi nó cần ghi dữ liệu vào một cổng của 8255.

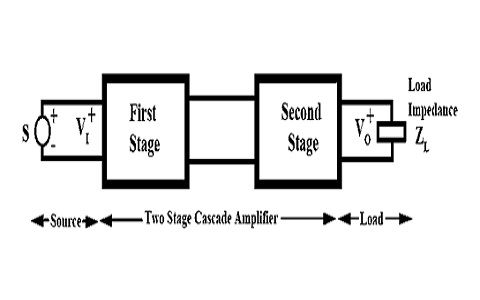

8255 truyền dữ liệu bằng bus dữ liệu 8 bit tới bộ vi xử lý 8086. Giao thức truyền thông nối tiếp được sử dụng để truyền thông giữa 8086 & 8255. Hai đường địa chỉ A1 & A0 được sử dụng để thực hiện các lựa chọn bên trong 8255. Các chân bus dữ liệu của 8255 như D0 đến D7 được kết nối với các đường dữ liệu của bộ vi xử lý 8086, các chân đầu vào đọc như RD' & các chân đầu vào ghi như WR' được kết nối với I/O read và I/O write của 8086.

Họ có bốn cổng chính để chọn PA, PB, PC & điều khiển từ. Các cổng này chủ yếu được sử dụng để truyền dữ liệu và từ điều khiển được chọn để gửi tín hiệu. Hai tín hiệu được gửi đến 8255 là tín hiệu I/O và tín hiệu BSR. Tín hiệu I/O được sử dụng để khởi tạo chế độ & hướng của các cổng trong khi BSR hữu ích để cài đặt và đặt lại đường tín hiệu.

Trong thiết bị sau, giả sử thiết bị được kết nối là thiết bị đầu vào. Lúc đầu, thiết bị này xin phép PPI để có thể truyền dữ liệu.

8255 PPI cho phép các thiết bị Đầu vào truyền dữ liệu, bất cứ khi nào không còn dữ liệu nào bên trong 8255, dữ liệu này phải được truyền tới bộ xử lý 8086. Nếu 8255 PPI có một số dữ liệu còn lại trước đó thì nó vẫn chưa được gửi đến bộ vi xử lý 8086, sau đó nó không cho phép thiết bị Đầu vào.

Khi 8255 PPI cho phép thiết bị đầu vào, thì dữ liệu được lấy và lưu trữ trong các thanh ghi tạm thời của 8255 PPI. Khi 8255 PPI chứa một số dữ liệu, thì dữ liệu đó phải được truyền đến bộ vi xử lý 8086, sau đó truyền tín hiệu đến PPI.

Khi bộ vi xử lý 8086 được tự do lấy thông tin, thì 8086 sẽ truyền lại tín hiệu, sau đó quá trình truyền dữ liệu xảy ra giữa 8255 và 8086. Nếu bộ vi xử lý 8086 không được rảnh trong một thời gian dài, điều đó có nghĩa là 8255 PPI bao gồm một số giá trị không được gửi đến bộ vi xử lý 8086, do đó 8255 PPI không cho phép thiết bị Đầu vào truyền bất kỳ dữ liệu nào vì dữ liệu hiện có sẽ bị ghi đè. Tín hiệu mũi tên cong được thể hiện trong sơ đồ trên được gọi là tín hiệu bắt tay. Vì vậy, quá trình truyền dữ liệu này được gọi là bắt tay.

Các yếu tố cần xem xét khi giao tiếp với 8255

Có nhiều điều cần xem xét khi giao tiếp với 8255 sẽ được thảo luận dưới đây.

- Các cổng của 8255 ở trạng thái chưa được lập trình là các cổng đầu vào vì nếu chúng là các cổng o/p trong trạng thái chưa được định cấu hình, bất kỳ thiết bị i/p nào cũng được kết nối với nó – thiết bị đầu vào cũng sẽ tạo ra đầu ra trên các dòng cổng và 8255 cũng sẽ tạo ra một đầu ra. Khi hai đầu ra được gắn với nhau, nó sẽ dẫn đến việc một/cả hai thiết bị bị hỏng.

- Các chân đầu ra của 8255 không thể được sử dụng để cấp nguồn cho các thiết bị vì chúng không có khả năng cung cấp dòng điện cần thiết.

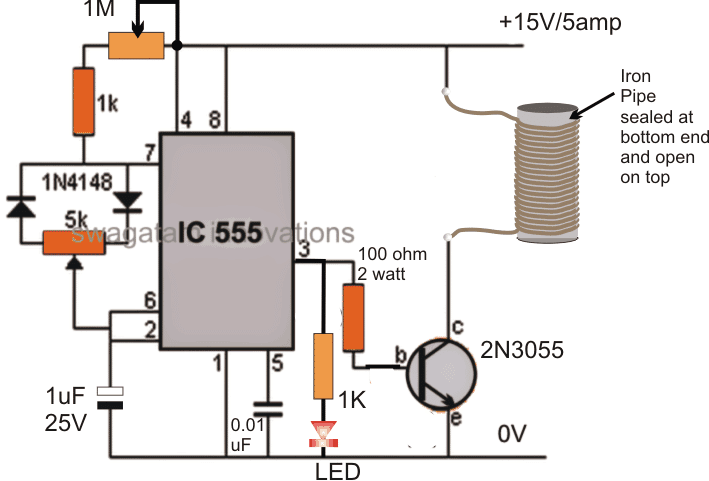

- Bất cứ khi nào động cơ hoặc đèn hoặc loa được kết nối với 8255 thì cần kiểm tra định mức hiện tại của thiết bị & 8255.

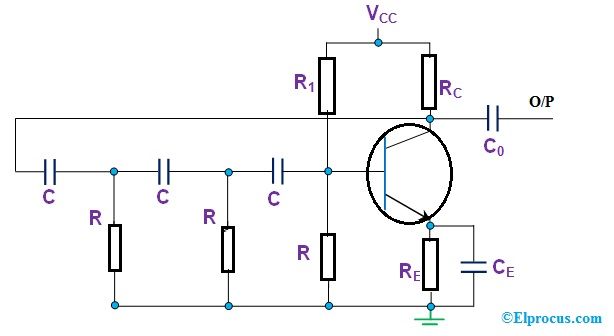

- Khi 8255 không có khả năng cung cấp dòng điện cần thiết, hãy sử dụng đảo ngược như 7406 và bộ khuếch đại không đảo giống 7407. Khi yêu cầu dòng điện lớn, bóng bán dẫn có thể được sử dụng trong cấu hình của một cặp Darlington.

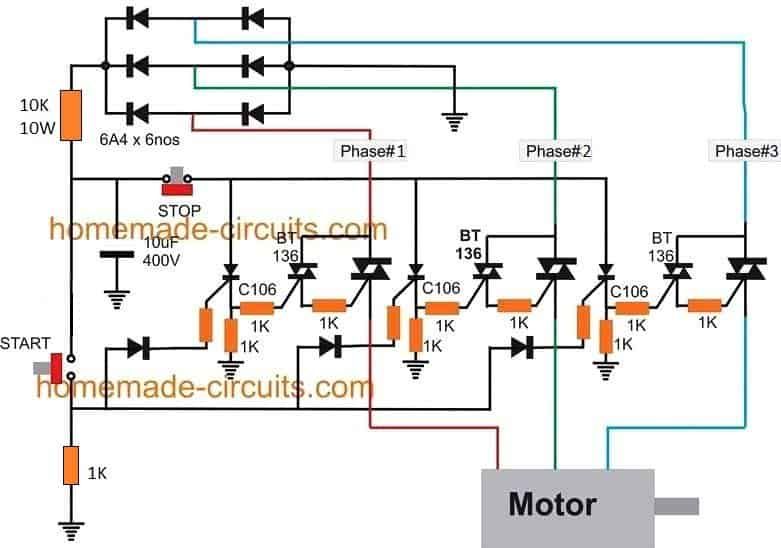

- Bất cứ khi nào động cơ điện một chiều được giao tiếp với 8255 thì chọn phù hợp Cầu chữ H dựa trên đặc điểm kỹ thuật của động cơ vì cầu H sẽ cho phép động cơ DC chạy theo bất kỳ hướng nào.

- Cổng A & Cổng B chỉ có thể được sử dụng làm cổng 8 bit, do đó tất cả các chân của các cổng này phải là đầu vào hoặc đầu ra.

- Khi các thiết bị cấp nguồn AC được kết nối với 8255 thì một tiếp sức phải được sử dụng để bảo vệ.

- Khi Cổng A & B được lập trình trong Chế độ 1 hoặc Chế độ 2 thì Cổng C không thể hoạt động như một cổng I/O bình thường.

Thuận lợi

Các Ưu điểm của bộ vi xử lý 8255 bao gồm những điều sau đây.

- Bộ vi xử lý 8255 có thể được sử dụng với hầu hết mọi bộ vi xử lý.

- Các cổng khác nhau có thể được chỉ định làm chức năng I/O.

- Nó hoạt động với nguồn điện được điều chỉnh + 5V.

- Nó là một bộ đồng xử lý được sử dụng phổ biến.

- Bộ đồng xử lý 8255 hoạt động như một giao diện giữa bộ vi xử lý và các thiết bị ngoại vi để truyền dữ liệu song song.

Các ứng dụng

Các Ứng dụng của bộ vi xử lý 8255 bao gồm những điều sau đây.

- Bộ vi xử lý 8255 được sử dụng để kết nối thiết bị ngoại vi & đèn LED hoặc tiếp sức giao diện, Giao diện động cơ bước , Giao diện hiển thị, Giao diện bàn phím, Giao diện ADC hoặc DAC, Bộ điều khiển tín hiệu giao thông, Bộ điều khiển thang máy, v.v.

- 8255 là một thiết bị giao diện ngoại vi có thể lập trình được sử dụng phổ biến.

- Bộ vi xử lý này được sử dụng để truyền dữ liệu trong các điều kiện khác nhau.

- Nó được sử dụng để giao tiếp với động cơ bước & động cơ DC.

- Bộ vi xử lý 8255 được sử dụng rộng rãi trong các hệ thống vi điều khiển hoặc máy vi tính khác nhau cũng như máy tính gia đình như tất cả các mẫu MSX & SV-328.

- Bộ vi xử lý này cũng có thể được sử dụng trong PC/XT, IBM-PC, PC/jr gốc & bản sao với nhiều máy tính gia đình khác nhau như N8VEM.

Như vậy, đây là tổng quan về bộ vi xử lý 8255 – kiến trúc, làm việc với các ứng dụng. Bộ vi xử lý 82C55 là một thiết bị I/O có thể lập trình cho mục đích chung, được sử dụng với các bộ vi xử lý khác nhau. Cấu hình tiêu chuẩn công nghiệp với bộ vi xử lý hiệu suất cao 82C55 rất phù hợp với 8086. Đây là câu hỏi dành cho bạn, bộ vi xử lý là gì? bộ vi xử lý 8086 ?